- 您现在的位置:买卖IC网 > Sheet目录3872 > PIC16C57C-04/SP (Microchip Technology)IC MCU OTP 2KX12 28DIP

PIC18F2450/4450

2006 Microchip Technology Inc.

Advance Information

DS39760A-page 129

14.0

UNIVERSAL SERIAL BUS

(USB)

This section describes the details of the USB peripheral.

Because of the very specific nature of the module,

knowledge of USB is expected. Some high-level USB

information is provided in Section 14.9 “Overview of

USB” only for application design reference. Designers

are encouraged to refer to the official specification

published by the USB Implementers Forum (USB-IF) for

the latest information. USB Specification Revision 2.0 is

the most current specification at the time of publication

of this document.

14.1

Overview of the USB Peripheral

The PIC18F2450/4450 device family contains a full-

speed and low-speed compatible USB Serial Interface

Engine (SIE) that allows fast communication between

any USB host and the PIC microcontroller. The SIE can

be interfaced directly to the USB, utilizing the internal

transceiver, or it can be connected through an external

transceiver. An internal 3.3V regulator is also available

to power the internal transceiver in 5V applications.

Some special hardware features have been included to

improve performance. Dual port memory in the

device’s data memory space (USB RAM) has been

supplied to share direct memory access between the

microcontroller core and the SIE. Buffer descriptors are

also provided, allowing users to freely program

endpoint memory usage within the USB RAM space.

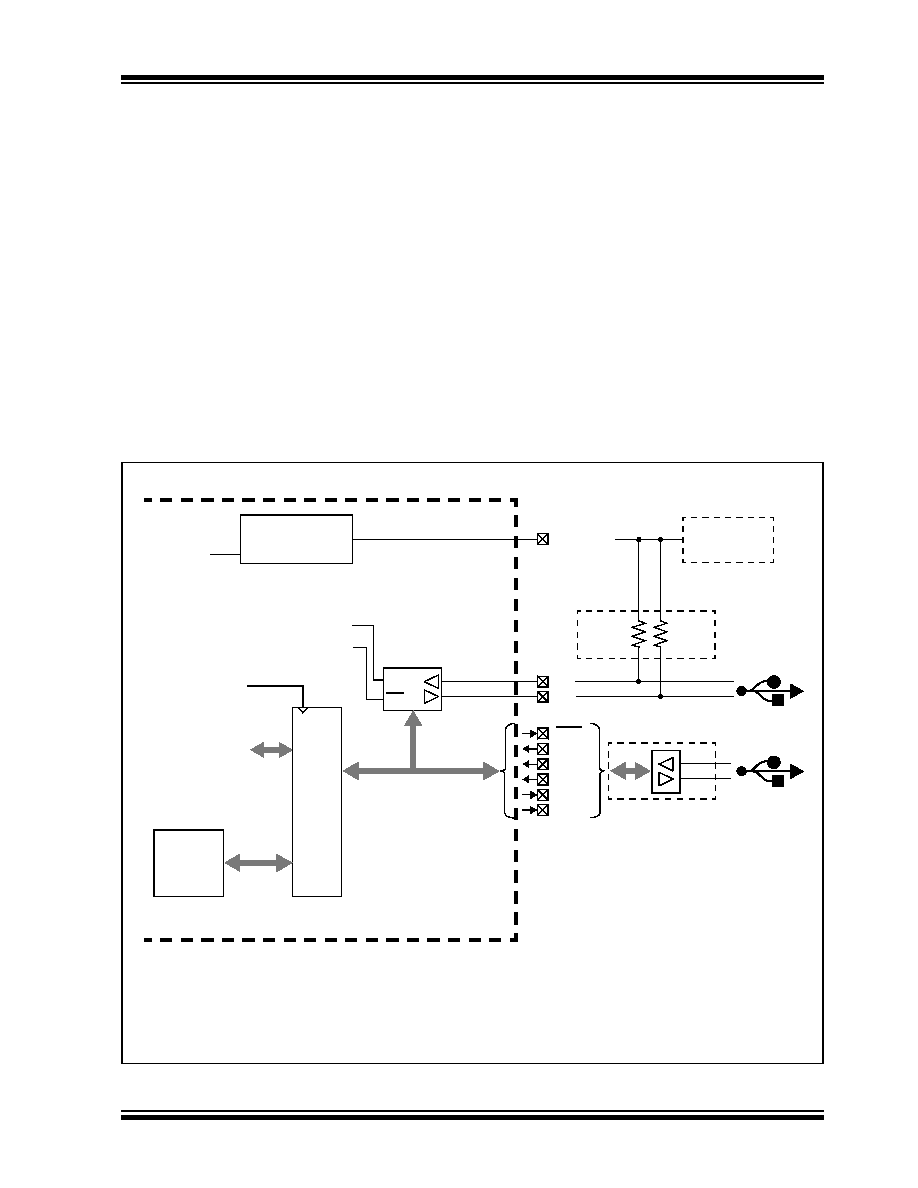

Figure 14-1 presents a general overview of the USB

peripheral and its features.

FIGURE 14-1:

USB PERIPHERAL AND OPTIONS

UOE(1)

256-Byte

USB RAM

USB

SIE

USB Control and

VM(1)

VP(1)

RCV(1)

VMO(1)

VPO(1)

Transceiver

External

Transceiver

EN

3.3V Regulator

D+

D-

OE

VUSB

External 3.3V

Supply(3)

FSEN

UTRDIS

USB Clock from the

Oscillator Module

Configuration

VREGEN

External

Pull-ups(2)

(Low

(Full

PIC18F2450/4450 Family

USB Bus

FS

Speed)

Note 1:

This signal is only available if the internal transceiver is disabled (UTRDIS = 1).

2:

The pull-ups can be supplied either from the VUSB pin or from an external 3.3V supply.

3:

Do not enable the internal regulator when using an external 3.3V supply.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16LF628A-I/SO

IC MCU FLASH 2KX14 EEPROM 18SOIC

PIC16C55A-20/SO

IC MCU OTP 512X12 28SOIC

PIC24F16KA101-I/MQ

IC PIC MCU FLASH 16KB 20-QFN

PIC16F627-04/SO

IC MCU FLASH 1KX14 COMP 18SOIC

PIC16C58B-20I/P

IC MCU OTP 2KX12 18DIP

PIC24FJ16GA002-I/SS

IC PIC MCU FLASH 16K 28-SSOP

PIC16C55A-04I/SO

IC MCU OTP 512X12 28SOIC

PIC16CR77-I/ML

IC PIC MCU 8KX14 44QFN

相关代理商/技术参数

PIC16C57C-04/SP

制造商:Microchip Technology Inc 功能描述:IC 8BIT CMOS MCU 16C57 SDIL28

PIC16C57C-04/SP

制造商:Microchip Technology Inc 功能描述:Microcontroller IC Number of I/Os:20

PIC16C57C-04/SS

功能描述:8位微控制器 -MCU 3KB 72 RAM 20 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C57C-04E/P

功能描述:8位微控制器 -MCU 3KB 72 RAM 20 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C57C-04E/SO

功能描述:8位微控制器 -MCU 3KB 72 RAM 20 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C57C-04E/SP

功能描述:8位微控制器 -MCU 3KB 72 RAM 20 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C57C-04E/SS

功能描述:8位微控制器 -MCU 3KB 72 RAM 20 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C57C-04I/P

功能描述:8位微控制器 -MCU 3KB 72 RAM 20 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT